ECL-Bus-Decoder: Unterschied zwischen den Versionen

Chris (Diskussion | Beiträge) (Die Seite wurde neu angelegt: „ Da mir die Betriebsdatenerfassung unserer Wärmepumpe, die den zum Raumleitgerät zugehörigen Regler verwendet, nicht ganz [[Energieerfassung#W.C3.A4rmepumpe|ko…“) |

Chris (Diskussion | Beiträge) K (Platinenfotos, korrigierter Stromlaufplan Bus-Interface) |

||

| Zeile 1: | Zeile 1: | ||

| − | |||

Da mir die Betriebsdatenerfassung unserer Wärmepumpe, die den zum Raumleitgerät zugehörigen Regler verwendet, nicht ganz [[Energieerfassung#W.C3.A4rmepumpe|koscher]] war, hab ich diese Sache relativ schnell auf die Seite gelegt. Trotzdem hat es mir immer wieder in den Fingerspitzen gekribbelt, dem Gerät doch ein paar Kennwerte zu entlocken. | Da mir die Betriebsdatenerfassung unserer Wärmepumpe, die den zum Raumleitgerät zugehörigen Regler verwendet, nicht ganz [[Energieerfassung#W.C3.A4rmepumpe|koscher]] war, hab ich diese Sache relativ schnell auf die Seite gelegt. Trotzdem hat es mir immer wieder in den Fingerspitzen gekribbelt, dem Gerät doch ein paar Kennwerte zu entlocken. | ||

| Zeile 9: | Zeile 8: | ||

</gallery> | </gallery> | ||

| − | Das Signal besteht aus einem | + | Das Signal besteht aus einem 50Hz Rechtecksignal, wobei der Duty-Cycle etwa 36/64 ist. |

| − | Nutzinformationen selbst werden in der Low-Phase des (ich nenne es einfach mal) Trägersignals übermittelt. | + | Nutzinformationen selbst werden in der Low-Phase des (ich nenne es einfach mal) Trägersignals übermittelt. In dessen Low-Phasen (7,28ms) werden die Daten mit einer Bitlänge von 428µs übertragen. Also können in dieser Zeit 17 Bit übertragen werden, wobei das erste immer 0 ist. |

| − | Da ich mit meinem Oszilloskop leider | + | Da ich mit meinem Oszilloskop leider keinen vollständigen Datensatz einfangen konnte und mein Logic-Analyzer wohl auch zu kurzspeichrig ist, werde ich wohl einen alten PC als primitivst-Oszi verwenden, zumal die Frequenzen für die Soundkarte kein Problem darstellen sollten. |

| + | Wie im Blog [http://hobbyelektronik.org/b/?p=386 erwähnt] bin ich durch einen (un)glücklichen Zufall an ein [http://de.fernwaerme.danfoss.com/xxTypex/17616_MNU17407524.html ECA60] von Danfoss gekommen. | ||

| − | + | Um die Entwicklung eines Businterfaces zu vereinfachen, habe ich die Platine des Geräts fotografiert und per Bildbearbeitung übereinandergelegt: | |

| − | + | <gallery> | |

| + | Datei:ECL_ECA60-top.jpg|Oberseite | ||

| + | Datei:ECL_ECA60-top.jpg|Unterseite (gespiegelt) | ||

| + | </gallery> | ||

| − | |||

Mit etwas Buntstift und überlegen entstand in EAGLE folgender Stromlaufplan: | Mit etwas Buntstift und überlegen entstand in EAGLE folgender Stromlaufplan: | ||

| Zeile 30: | Zeile 32: | ||

Oben wird das Bussignal eingefüttert, an der mittleren CPU-Leitung liegt das auf Vcc + ~0,7V begrenzte Signal, das vom Bus empfangen wird. | Oben wird das Bussignal eingefüttert, an der mittleren CPU-Leitung liegt das auf Vcc + ~0,7V begrenzte Signal, das vom Bus empfangen wird. | ||

| − | Die obere und untere Leitung zur CPU dienen offensichtlich dem Senden auf dem Bus. | + | Die obere und untere Leitung zur CPU dienen offensichtlich dem Senden auf dem Bus. |

| + | Zuerst (siehe Historie des obigen Bildes) war ich etwas irritiert, warum T1 und T2 den Bus gegen sich selbst kurzschloss. Bis mir aufgefallen ist, dass da zur Spannungsglättung noch ein Elko an der Schaltung hängt. Das machte die Sache deutlich klarer: "Jeder" Teilnehmer im Bus sendet in den Low-Phasen des Trägersignals. | ||

| + | |||

| + | Wie T3 zum Senden von Daten verwendet werden soll, ist mir bis jetzt noch etwas schleierhaft. Bei den gemessenen 27Vss Busspannung würden die 48kOhm einen Strom von etwa 550µA verursachen. Der dürfte die Versorgungsspannung nur einbrechen lassen, wenn ihr Strom sehr stark begrenzt wird (was ich etwas bezweifel). | ||

Version vom 20. Februar 2011, 15:13 Uhr

Da mir die Betriebsdatenerfassung unserer Wärmepumpe, die den zum Raumleitgerät zugehörigen Regler verwendet, nicht ganz koscher war, hab ich diese Sache relativ schnell auf die Seite gelegt. Trotzdem hat es mir immer wieder in den Fingerspitzen gekribbelt, dem Gerät doch ein paar Kennwerte zu entlocken.

In der Bedienungsanleitung der Anlage entdeckte ich ein paar Schaltpläne, in denen ein externes Sensor-/Alarmmodul samt Busanbindung zu finden war. Die Recherche nach dem mit ECL betitelte Bus lieferte bis auf ein paar kommerzielle Datenwandler keine brauchbaren Ergebnisse - also schnappte ich mir das Oszilloskop und versuchte auf eigene Faust, dem Teil etwas zu entlocken:

Das Signal besteht aus einem 50Hz Rechtecksignal, wobei der Duty-Cycle etwa 36/64 ist.

Nutzinformationen selbst werden in der Low-Phase des (ich nenne es einfach mal) Trägersignals übermittelt. In dessen Low-Phasen (7,28ms) werden die Daten mit einer Bitlänge von 428µs übertragen. Also können in dieser Zeit 17 Bit übertragen werden, wobei das erste immer 0 ist.

Da ich mit meinem Oszilloskop leider keinen vollständigen Datensatz einfangen konnte und mein Logic-Analyzer wohl auch zu kurzspeichrig ist, werde ich wohl einen alten PC als primitivst-Oszi verwenden, zumal die Frequenzen für die Soundkarte kein Problem darstellen sollten.

Wie im Blog erwähnt bin ich durch einen (un)glücklichen Zufall an ein ECA60 von Danfoss gekommen.

Um die Entwicklung eines Businterfaces zu vereinfachen, habe ich die Platine des Geräts fotografiert und per Bildbearbeitung übereinandergelegt:

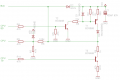

Mit etwas Buntstift und überlegen entstand in EAGLE folgender Stromlaufplan:

Oben wird das Bussignal eingefüttert, an der mittleren CPU-Leitung liegt das auf Vcc + ~0,7V begrenzte Signal, das vom Bus empfangen wird. Die obere und untere Leitung zur CPU dienen offensichtlich dem Senden auf dem Bus. Zuerst (siehe Historie des obigen Bildes) war ich etwas irritiert, warum T1 und T2 den Bus gegen sich selbst kurzschloss. Bis mir aufgefallen ist, dass da zur Spannungsglättung noch ein Elko an der Schaltung hängt. Das machte die Sache deutlich klarer: "Jeder" Teilnehmer im Bus sendet in den Low-Phasen des Trägersignals.

Wie T3 zum Senden von Daten verwendet werden soll, ist mir bis jetzt noch etwas schleierhaft. Bei den gemessenen 27Vss Busspannung würden die 48kOhm einen Strom von etwa 550µA verursachen. Der dürfte die Versorgungsspannung nur einbrechen lassen, wenn ihr Strom sehr stark begrenzt wird (was ich etwas bezweifel).